Master Thesis

# Operational Characterization of Weak Memory Consistency Models

Maximilian Senftleben

March 26, 2013

Department of Computer Science, University of Kaiserslautern, D 67653 Kaiserslautern, Germany

Examiner: Prof. Dr. Klaus Schneider Dipl.-Technoinform. Daniel Baudisch

# Eigenständigkeitserklärung

Hiermit versichere ich, dass ich die von mir vorgelegte Arbeit mit dem Thema "Operational Characterization of Weak Memory Consistency Models" selbstständig verfasst habe, dass ich die verwendeten Quellen und Hilfsmittel vollständig angegeben habe und dass ich die Stellen der Arbeit - einschließlich Tabellen und Abbildungen -, die anderen Werken oder dem Internet im Wortlaut oder dem Sinn nach entnommen sind unter Angabe der Quelle als Entlehnung kenntlich gemacht habe.

Kaiserslautern, den 26. März 2013

Maximilian Senftleben

#### Abstract

This thesis deals with the most common memory consistency models and provides comparable definitions for some of them. The relationship between these models is analysed and the difference between them explained by providing characterising examples. The primary focus of this thesis is to provide operational semantics for the most relevant consistency models. This is achieved by implementing machines which are based on the consistency model definitions using the synchronous programming language Quartz. The provided implementations are constructed to conform with the corresponding definitions in terms of correctness and completeness. The latter property, completeness, is desirable for further work which may aim on reducing more sophisticated implementations on the constructed ones to show their correctness.

#### Zusammenfassung

Diese Arbeit behandelt die meistgebräuchlichsten Speicherkonsistenzmodelle und gibt vergleichbare Definition für einige dieser. Die Beziehungen der Modell wird analysisert und derren Unterschiede mittels charakterisierender Beispiele erklärt. Der primäre Fokus der Arbeit ist die Bereitstellung von ausführbarer Semantik für die relevantesten Konsistenzmodelle. Dies wird erreicht durch die Implementierung von Maschinen, welche auf den Definitionen der Speichermodelle basieren, unter der Verwendung der synchronen Programmiersprache Quartz. Die vorgestellten Implementierungen wurden sowohl hinsichtlich Korrektheit als auch Vollständigkeit anhand der zugehörigen Definitionen erstellt. Die Vollständigkeitseigenschaft ist interessant um in möglicher künftiger Arbeit den Versuch unternehmen zu können ausgeklügeltere Implementierung auf eine der vorgestellten zurückzuführen um deren Korrektheit zu zeigen.

# Contents

| 1. | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                                                                                                                                                                                                       |

|----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2. | Related Work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5                                                                                                                                                                                                       |

| 3. | Consistency Models3.1. Local Consistency (LC)3.2. Slow Consistency3.3. Pipelined-RAM (PRAM) Consistency / Global Process Order (GPO)3.4. PRAM-M Consistency3.5. Cache Consistency (CC) / Global Data Order (GDO)3.6. Global Write-read-write Order (GWO)3.7. Global Anti-Order (GAO)3.8. Causal Consistency / GPO+GWO3.9. Processor Consistency by Goodman (PC-G)3.10. GPO + GDO Consistency3.11. Processor Consistency by DASH (PC-D)3.12. Partial Store Ordering (PSO)3.14. Sequential Consistency (SC)3.15. Overview/Relationship | <ul> <li>7</li> <li>8</li> <li>8</li> <li>10</li> <li>11</li> <li>12</li> <li>13</li> <li>14</li> <li>15</li> <li>15</li> <li>17</li> <li>18</li> <li>19</li> <li>20</li> <li>21</li> <li>23</li> </ul> |

| 4. | Reference Machines4.1. Common Structural Elements4.2. Local Consistency Reference Machine4.3. Slow Consistency Reference Machine4.4. PRAM Consistency Reference Machine4.5. Cache Consistency Reference Machine4.6. Causal Consistency Reference Machine4.7. Processor (PC-G) Consistency Reference Machine4.8. PSO Consistency Reference Machine4.9. TSO Consistency Reference Machine4.10. Sequential Consistency Reference Machine                                                                                                | <b>31</b> 31 33 35 36 38 40 43 45 45 45 46                                                                                                                                                              |

| 5. | Implementations         5.1. Environment         5.2. Interface         5.3. Non-Determinism         5.4. (Un)Bounded Buffer         5.5. Improvements                                                                                                                                                                                                                                                                                                                                                                               | <b>49</b><br>49<br>49<br>49<br>49<br>50                                                                                                                                                                 |

| 6.  | Conclusions and Further Work                                  | 51 |  |  |  |

|-----|---------------------------------------------------------------|----|--|--|--|

| Α.  | Quartz Implementations                                        | 53 |  |  |  |

|     | A.1. Remarks                                                  | 53 |  |  |  |

|     | A.2. Shared modules                                           | 53 |  |  |  |

|     | A.3. RefLocal : Local Consistency Reference Machine           | 60 |  |  |  |

|     | A.4. RefSlow : Slow Consistency Reference Machine             | 62 |  |  |  |

|     | A.5. RefPRAM : PRAM Consistency Reference Machine             | 64 |  |  |  |

|     | A.6. RefCache : Cache Consistency Reference Machine           | 66 |  |  |  |

|     | A.7. RefCausal : Causal Consistency Reference Machine         | 67 |  |  |  |

|     | A.8. RefProcessor : PC-G Consistency Reference Machine        |    |  |  |  |

|     |                                                               |    |  |  |  |

|     | A.10.RefTSO : TSO Consistency Reference Machine               | 74 |  |  |  |

|     | A.11.RefSequential : Sequential Consistency Reference Machine | 76 |  |  |  |

| Bil | Bibliography                                                  |    |  |  |  |

# 1. Introduction

With multiprocessor systems, the historical assumption of a sequential consistent memory system becomes more and more a bottleneck for memory latency. While some programs rely on sequential consistency, many programs could execute properly with weaker consistency constraints and therefore justify the research of such models.

Historically, a computer architecture was considered to consist of a single processing unit and a single memory connected via a single bus (Von Neumann architecture 1945). The single bus enforces that each memory read operation returns the value most recently written to that location. Even if the processor alternatingly executes multiple processes, the memory operations take place one after the other and form a sequence.

Nowadays a computer architecture may consist of multiple processors which share a common main memory. Early multiprocessor systems connected multiple processors via a single bus to a shared memory such that processors had to compete for bus access. Therefore the memory operations of all processes formed a sequence as well. Newer multiprocessor systems became more complex as the individual processors started to cache memory operations or otherwise tried to increase their performance. In distributed systems, the assumption of a single memory is given up in favor of multiple memories which are shared between all processors as so called distributed shared memory.

Multiple processes interact via shared memory to synchronize with each other. For instance, if two processes share a resource which only may be accessed by one process at a time, then it must be ensured that one process does not use the resource if it is already in use by the other one. As an example, the following simple program tries to solve that problem:

```

bool p1_in_cs, p2_in_cs;

```

| process P1 {                 | process P2 {             |

|------------------------------|--------------------------|

| $if(p2\_in\_cs == false) $ { | $if(p1_in_cs = false)$ { |

| $p1\_in\_cs = true;$         | $p2\_in\_cs = true;$     |

| critical_operations;         | $critical_operations;$   |

| $p1\_in\_cs = false;$        | $p2\_in\_cs = false;$    |

| }                            | }                        |

| }                            | }                        |

The problem that may occur is that process P1 reads variable  $p2\_in\_cs = false$ , then P2 reads variable  $p1\_in\_cs = false$  and then both enter the critical section, both assuming that they are the only one.

This problem is called the mutual exclusion problem and was first correctly solved by T.J. Dekker and presented by E.W. Dijkstra in 1965 [Dijk68]. The resulting algorithm, known as Dekker's algorithm, is as follows:

```

// initially false

bool flag1, flag2, turn;

process P1 {

process P2 {

flag2 = true;

flag1 = true;

while (flag 2 = true) {

while (flag1 == true) {

if (turn != false) {

if(turn != true) {

flag1 = false;

flag2 = false;

while (turn != false) {}

while (turn != true) {}

flag1 = true;

flag2 = true;

}

}

}

}

critical_operations;

critical_operations;

turn = false;

turn = true;

flag0 = false;

flag1 = false;

noncritical_operations;

noncritical_operations;

}

}

```

This algorithm enables a process to detect when an other process has the intention to enter or currently resides in the critical section. If both processes did not enter the critical section yet then the algorithm determines which process may proceed and which one has to wait using variable *turn*.

Dekker's algorithm works for multi-threaded uniprocessor and the mentioned single-bus-based multiprocessor systems, but it may fail on other multiprocessor systems, e.g. systems with processors that buffer memory operations in write-back caches, if no further constraints for the memory systems are given. In such a system, both process P1 and P2 may set their flag variable to true but both keep the write operation in their cache and read the value of the other's flag variable from main memory as false. As a consequence both processes enter the critical section. Dekker's algorithm failed for the considered multiprocessor system.

There are two ways to handle this problem:

- Either the multiprocessor system's memory management must be modified to behave equivalent to a multi-threaded uniprocessor. This behaviour is called sequential consistency and if a multiprocessor system provides sequential consistent behaviour then Dekker's algorithm works as intended. A technique to enable multiprocessor systems which use write-back caches to provide sequential consistent behaviour is the so called MESI protocol [PaPa98]. MESI is named after the four states each cache line can have: Modified, Exclusive, Shared, and Invalid. Variations of MESI are used in many modern CPUs, e.g. Intel's Pentium 4 [IA313].

- An alternative way to handle the problem is to accept that there may exist multiprocessor systems with non-sequential memory behaviour. To utilise these systems despite their lack of sequential consistency, each system has to define its memory behaviour. These definitions can act as some sort of interface that guarantees programmers the cor-

rect execution of their programs. Such interfaces are called memory consistency models and determine which relaxations or optimizations are possible and in which way the system behaves different to a sequential consistent one.

A memory consistency model can be defined in different ways. It can be defined in an operational way by providing a machine structure and related interconnection rules or by revealing an implementation of such a system. For instance, Lipton and Sandberg [LiSa88] provided an implementation for PRAM by defining its structure and communication rules. The consistency model of such a machine is defined as the set of executions it may produce for given programs.

A method of defining a consistency model indirectly is to define a set of rules for programmers to ensure sequential consistency, for example with Sequential Consistency Normal Form (SCNF) by Adve [Adve93]. An implementation of a memory system complies with the consistency model if each program satisfying the given rules is guaranteed to behave like a sequential consistent system. This type of definition has the benefit that if a given system can be optimized in a way that programs which respect the definition's rules still behave sequential consistent, then the optimized version can replace the prior version without requiring the programmer to make adjustments.

Another way of defining a consistency model is to define which ordering of memory operations the memory and processes are allowed to observe. One possibility is to define the model by providing rules which must be satisfied by the ordering of all operations as observed by the main memory. For example this is done for the SPARC memory models TSO and PSO in an axiomatic way. This is done by providing 6 axioms (TSO) respectively 7 axioms (PSO) which if satisfied by an ordering on all memory operations imply a consistent execution. Yet another possibility is a view-based definition which defines rules on the ordering of each process' own operations and others' write operations. Such definitions (e.g. given by Steinke and Nutt in [StNu04]) allow a simple comparison of different memory models and abstract from the inner structure of memory systems.

Weak memory models emerged from the endeavours to optimize the latency of memory systems. Improvements weakened the underlying sequential model in a way that some inconsistent states became reachable. These improvements and new concepts became new weak memory models. To use the benefits of the new models they must be defined in a way that programmers can write or adjust their programs such that potential inconsistent states of the memory system are avoided and the executions produce the intended results.

In this thesis, some known consistency models described in the literature [ABHN91, BaBe97, Good91, HuAh90, Lamp79, LiSa88, SPAR91] are characterized in an operational manner by specifying reference machines. These reference machines are obtained by deriving memory system implementations directly from the consistency model definitions. The resulting reference machines do not aim to be efficient but try to be as minimalistic as possible (in terms of different components and structures, not necessarily size) to simplify verification of correctness and completeness of the implementation.

Apart from the benefit of such easy-to-understand definitions of different memory consistency models for educational purposes, such reference machines may be the basis of attempts to classify or verify the consistency class of an arbitrary memory system.

#### 1. Introduction

# 2. Related Work

Most parts of this thesis are based on the Unified Theory of Shared Memory Consistency by Steinke and Nutt [StNu04] which offers view-based definitions for many common memory consistency models. Furthermore it reveals underlying properties which suffice to describe the presented models.

Similar to this work Higham, Kawash and Verwaal [HiKV98] provided definitions and comparisons of some consistency models and defined machines for the models. Their implementations lack some details (e.g. "switch" functionality) and the work leaves some questions unanswered (e.g. sizes of FIFOs).

[BaBe97] characterizes different consistency models in a view based way for non-synchronized ("pure") memory models and presents formal definitions for some synchronized ("hybrid") memory models as well. Ahamad et al. [ABJK<sup>+</sup>93] compares different view-based definitions of processor consistency by Goodman and the DASH system.

Sindhu, Frailong and Cekleov [SiFC92] present a formal framework for axiomatic definitions of memory consistency models and provide definitions for sequential, PSO and TSO consistency.

[Mosb93a] gives a brief overview of some weak memory models and discusses their influence on programming language and compiler design. Adve [Adve93] provides sequential consistency normal form, a programmer-centric approach to specify memory models. Adve and Hill [AdHi93] describe a shared-memory model that guarantees sequential consistency for datarace-free programs and which unifies four earlier models. Adve and Gharachorloo [AdGh96] give an overview over memory consistency related issues, describe existing and possible relaxations of a sequential consistency.

In [BoPe09] an approach to formalize a memory model as a part of weak operational semantics is presented and proved to work as intended for data-race free programs.

Loewenstein et al. [LoCM06] presents a technique to verify a memory model's (TSO) behaviour against its axiomatic definition. Linden and Wolper [LiWo11] describe an approach to memory fence insertion in programs to execute correctly under weak memory systems (TSO,PSO) based on verification techniques (finite state automata based verification tool). The TSOtool described by Hangal et al. [HVML<sup>+</sup>04] offers a test platform to check pseudorandomly generated test programs run on a memory system against the TSO specification.

Owens et al. describe x86-TSO [OwSS09], a new model for x86 processors which is based on the SPARCv8 TSO model [SPAR91]. Sewell et al. [SSON+10] present and compare x86-TSO with recent Intel and AMD specifications and address data-race-freedom for x86-TSO.

#### 2. Related Work

# 3. Consistency Models

Consistency models can be defined by the set of executions they allow for a given set of processes.

In the following section, a formalism for specifying memory models is introduced, formal definitions of common memory consistency models are given, and their relationships are analysed.

To argue about memory models, a formalism is needed which is able to cover all aspects of a memory operation:

- access mode (read, write)

- issuer (process issuing the operation)

- location (memory address)

- value

The following "view"-based formalism is taken from Steinke and Nutt which itself is based on Ahamad et al. [ABJK<sup>+</sup>93] and Bataller and Bernabeu [BaBe97]: A "view"-based definition focuses on the view of a process with respect to the memory system. If a process can observe a behaviour which conflicts with the consistency properties, then the execution may be rejected. This kind of definition does not give any implementation details but only requires the system to provide a view for each connected process which satisfies the consistency properties.

#### Definition 3.1 (Shared Memory Formalism). [StNu04, Appendix A]

An execution is a set of processes P, a set of shared variables V, a set of operations O, and two partial orders on O: process order  $<_{PO}$ , and writes-to order  $\mapsto$ .

An **operation** is a tuple (op,i,x,v) where  $op \in \{r, w\}$  (read,write),  $i \in P, x \in V$ , and v is a valid value for x. The operation  $(w, \epsilon, x, \perp)$  is called the **initial write** of x.

Several functions are defined on the operation tuple: type(o) returns the type of operation o, var(o) returns the variable of operation o, val(o) returns the value of an operation o and proc(o) returns the process of operation o.

Local order for process of operation of  $\left(\forall_{o_j,o_k\in(r,*,*,*)}(o_j<_i o_k\oplus o_k<_i o_j)\right) \wedge \left(\forall_{x\in V,o\in(*,i,*,*)}(w,\epsilon,x,\perp)<_i o\right).$ Process order  $<_{PO}$  is a relation such that  $<_{PO} = \bigcup_{i\in P} <_i.$ Writes-to order  $\mapsto$  is a relation such that  $\forall_{o\in(r,*,*,*)} \exists_{i\in P} [(w,i,var(o),val(o)) \mapsto o].$ A relation  $<_{serial}$  is a serial view SerialView (< |O') on operations  $O' \subseteq O$  which respects < iff < iff $< \subseteq <_{serial} \land \forall_{o_1, o_2 \in O'} (o_1 <_{serial} o_2 \oplus o_2 <_{serial} o_1) \text{ and}$  $\forall_{r \in O'} \exists_{w \in O'} (w \mapsto r \land w <_{serial} r \land \not\exists_{w_2 \in O'} (var(w_2) = var(r) \land w <_{serial} w_2 <_{serial} r))$

In this formalism, an execution represents the result and context of multiple processes (P) that issue operations (O) on shared variables (V) to a memory system. Each operation is assigned to a single process and is either a read from a given memory address or a write with a target address and value. The formalism defines three orders: 1) the local order ( $<_i$ ) defines the sequence in which operations of a single process (i) are issued to the memory system, 2) the process order is the union of all processes' local orders, and 3) the writes-to order orders each read operation after a write operation which writes the value to the memory the read operation reads. Important for the following definitions is the notion of a serial view. A serial view (SerialView) on an execution is a total order (view) on a subset of the execution's operations which represents the order in which the process sees the memory operations. A read in a serial view must read from the most recent preceding write to the same variable (serial).

## 3.1. Local Consistency (LC)

Local consistency was first defined by Heddaya and Sinha [HeSi92] as the weakest constraint that could be required of a shared memory system. It requires that each process observes all operations as if they were executed on a single processor. It enforces that a process' write can be observed by itself.

Local Consistency [HeSi92, BaBe97] is defined by Steinke and Nutt [StNu04, Theorem 3.8] as follows:

Definition 3.2. An execution is locally consistent iff

$\forall_{i \in P} \exists SerialView (<_i | (*, i, *, *) \cup (w, *, *, *))$

An execution is locally consistent iff each process observes operations in a serial view which orders its own operations in program order and other processes' write operations in an arbitrary order.

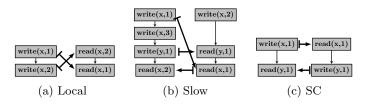

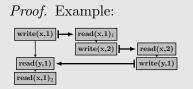

**Example** Figure 3.1a shows an execution which is locally consistent because of the existence of the following SerialViews:

[P1]: write(x,1), write(x,2)

[P2]: write(x,2), read(x,2), write(x,1), read(x,1)

Remark: The example is not slow consistent which is shown later.

#### 3.2. Slow Consistency

Hutto and Ahamad [HuAh90] introduced slow consistency to eliminate consistency maintenance which leads to high latency. Having other weak memory models in mind they showed that even for their weaker model, slow consistency, techniques exist to solve the exclusion and dictionary problem. With those techniques, slow consistency may be used to increase

Figure 3.1.: Examples for locally, slowly, and sequentially consistent executions

memory latency for many multiprocess programs relying on the mentioned problems. Slowly consistent memory allows writes to propagate slowly to other processes.

Slow consistency [HuAh90] is defined as follows: A read returns a previously written value, and successive reads to the same location may not return writes issued earlier (by the process that issued the earlier write) than the read one. Furthermore, local writes must be visible immediately. Slow consistency is formally defined in Steinke and Nutt's formalism for shared memory consistency models [StNu04, Theorem 3.7]:

**Definition 3.3.** An execution is slowly consistent iff

$\forall_{i \in P, x \in V} \exists SerialView (<_{PO} | (*, i, x, *) \cup (w, *, x, *))$

An algorithm which solves the n-process exclusion problem for slowly consistent systems was provided by Hutto and Ahamad [HuAh90] and is given in pseudo-code as follows:

```

// initially false

process MutexServer {

bool[n] req,ack;

while(true) {

for (int i = 0 \dots n-1) {

if(req[i] == true) \{

process P_i {

req[i] = true;

req[i] = false;

while (ack[i] = false) {}

ack[i] = true;

while (ack[i] = true) \{\}

critical_operations;

ack[i] = false;

}

}

noncritical_ops;

}

}

}

```

**Example** Figure 3.1b shows an execution which is slowly consistent because the following SerialViews exist:

$\begin{array}{ll} [P1,x]: \text{ write}(\mathbf{x},1), \text{ write}(\mathbf{x},3), \text{ write}(\mathbf{x},2), \text{ read}(\mathbf{x},2) & [P1,y]: \text{ write}(\mathbf{y},1) \\ [P2,x]: \text{ write}(\mathbf{x},2), \text{ write}(\mathbf{x},1), \text{ read}(\mathbf{x},1), \text{ write}(\mathbf{x},3) & [P2,y]: \text{ write}(\mathbf{y},1), \text{ read}(\mathbf{y},1) \end{array}$

Remark: The example is neither PRAM nor cache consistent which is shown later.

Figure 3.1a is not slowly consistent because the  $\mapsto$  relation requires read(x,2) to happen after write(x,2) but read(x,1) to happen before write(x,2), which is not allowed due to  $read(x,2) <_{PO} read(x,1)$ .

# 3.3. Pipelined-RAM (PRAM) Consistency / Global Process Order (GPO)

One of the first common weak memory models described was PRAM (Pipelined RAM), which was presented 1988 by Lipton and Sandberg [LiSa88, LiSa94]. They show that their shared memory system PRAM scales better than sequentially consistent systems as it is immune to high network latency. Additionally, synchronization costs remain low while performance increases significantly.

Original PRAM [LiSa88] definition by Lipton and Sandberg [LiSa88]:

**Definition 3.4.** Consider *n* processes  $P_1, \ldots, P_n$  with a local memory  $M_1, \ldots, M_n$  each. Process *k* executes a read from location *i* "by performing a normal read from location *i*" of its own memory  $M_k$ . Process *k* executes a write to location *i* with value *v* "by performing a local action and initializing a global action. Locally, it does a normal write to  $[M_k]$  at location *i* with value *v*. Globally, it sends a message  $\langle i, v \rangle$  to all the other processors."

PRAM consistency (equivalent to GPO) based on the Steinke and Nutt [StNu04, Theorem 3.2, Definition 4.1] (which itself uses the definition of Ahamad et al. [ABJK<sup>+</sup>93]) is as follows:

Definition 3.5. An execution is PRAM consistent / Global Process Order (GPO) iff

$\forall_{i \in P} \exists SerialView \left( <_{PO} | (*, i, *, *) \cup (w, *, *, *) \right)$

In a PRAM consistent execution, every process observes the writes of an other process in the order they were issued. But two different processes may see writes of several processes in a different order.

A system implementing PRAM consistency therefore only has to assure that the communication from one process to another does not reorder or lose writes, while the transmission delay is not critical.

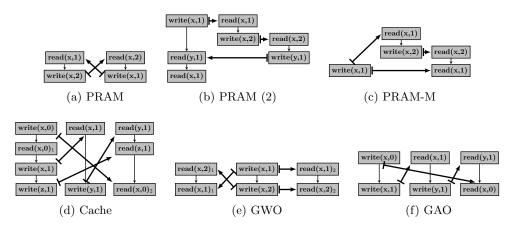

**Example** Figure 3.2a shows an execution which is PRAM consistent:

[P1]: write(x,1), read(x,1), write(x,2) [P2]: write(x,2), read(x,2), write(x,1)

Remark: The example is neither GWO nor cache consistent (and therefore neither causal nor processor consistent either) which is shown in the corresponding sections.

Figure 3.2b shows another execution which is PRAM consistent:

[P1]: write(x,2), write(x,1), write(y,1), read(y,1), read(x,1)

[P2]: write(x,1), read(x,1), write(x,2), write(y,1) [P3]: write(x,1), write(x,2), read(x,2), write(y,1) Remark: The example is however not PRAM-M consistent which is shown later.

Figure 3.1b is not PRAM consistent because the  $\mapsto$  relation requires the write(y,1) to happen before the read(y,1) and the read(x,1) before the write(x,3), which is not possible because write(x,3)  $<_{PO}$  write(y,1) and read(y,1)  $<_{PO}$  read(x,1).

Figure 3.2.: Examples for PRAM, cache, GWO, and GAO consistent executions

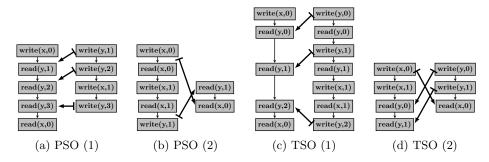

Figure 3.2d shows an execution which is not PRAM consistent because  $write(x,1) <_{PO} write(z,1) \mapsto read(z,1) <_{PO} read(x,0)_2$  implies write(x,1) appears before read(x,0) such that no SerialView exists for P3.

Figure 3.2e gives an example of an execution which is not PRAM consistent because the view P3 has on the writes of P2 does not comply with  $<_{PO}$ .

Figure 3.4a shows another example of an execution which is not PSO consistent because in a SerialView for P1 the following order on y would be required: read(y,1) < write(y,2) < read(y,2) < write(y,3) < read(y,3), but the constraints write(x,1) < write(y,3) < read(y,3) < read(y,3) < read(x,0) and write(x,0) < read(y,1) < write(y,2) < write(x,1) would not allow a SerialView respecting  $<_{PO}$ .

#### 3.4. PRAM-M Consistency

The informal definition (Definition 3.4) of PRAM consistency by Lipton and Sandberg [LiSa88] led to different interpretations which represent different consistency models. In contrast to the preceding definition of PRAM based on Ahamad et al., the definition of Mosberger [Mosb93b] assumes that a process k's write first updates the local memory  $M_k$  and afterwards broadcasts it to other processes and that reads are explicitly blocking. To distinguish this definition from the previous one, it is named PRAM-M in this thesis.

**Definition 3.6.** Two operations are ordered by local write-read-write order,  $o_1 <_{lwo}^{(i)} o_2$ , iff  $process(o_1) = i \land (o_1, o_2) \in (\mapsto \cup <_{PO})^*$  (\* means the transitive closure)

Definition 3.7. An execution is PRAM-M consistent iff

$$\forall_{i \in P} \exists SerialView \left( <_{PO} \cup <_{lwo}^{(i)} | (*, i, *, *) \cup (w, *, *, *) \right)$$

**Example** Figure 3.2c gives an example of a PRAM-M consistent execution:

[P1]: write(x,1), write(x,2) [P2]: write(x,1), read(x,1), write(x,2)

[P3]: write(x,2), read(x,2), write(x,1), read(x,1)

Remark: The example is however neither cache nor GWO consistent which is shown in the corresponding sections.

Figure 3.2b is not PRAM-M consistent as for P1 no SerialView exists as  $write(x,1) <_{lwo}^{(i)}$  $write(x,2) <_{lwo}^{(i)} write(y,1)$  conflicts with  $read(y,1) <_i read(x,1)$ .

# 3.5. Cache Consistency (CC) / Global Data Order (GDO)

In 1989 Goodman [Good91] provided a definition for cache consistency, which he called Weak Consistency as he implied that it would be the weakest form of consistency. Furthermore he mentioned that no synchronization guarantees would be possible with CC which is disproved by the existence of algorithms for exclusion even for slow consistency.

Cache consistency [Good91] and the equivalent GDO consistency are formally defined in Steinke and Nutt [StNu04, Theorem 3.3, Definition 4.4] as follows:

**Definition 3.8.** An execution is **cache consistent** iff  $\forall_{x \in V} \exists SerialView (<_{PO} | (*, *, x, *))$

**Definition 3.9.** Two operations are ordered by data order,  $o_1 <_{DO} o_2$ , iff  $var(o_1) = var(o_2)$  and either:  $o_1 <_{PO} o_2$  or  $o_1 \mapsto o_2$  or  $\exists_{r \in (r,*,*,*)} var(r) = var(o_1) \land val(r) \neq val(o_1) \land o_1 <_{PO} r \land o_2 \mapsto r$  or  $\exists_{o \in O} o_1 <_{DO} o <_{DO} o_2$

**Definition 3.10.** An execution is Global Data Order (**GDO**) iff:  $\forall_{i \in P} \exists SerialView (<_i \cup <_{DO} | (*, i, *, *) \cup (w, *, *, *))$

Each process observes the same ordering on memory operations regarding the same memory location, but processes may see operations regarding different memory locations in different orders.

**Example** Figure 3.2d shows an execution which is cache consistent:

[x]: write(x,0), read $(x,0)_1$ , read $(x,0)_2$ , write(x,1), read(x,1)

[y]: write(y,1), read(y,1) [y]: write(z,1), read(z,1)

[P1]: write(x,0), read(x,0)<sub>1</sub>, write(x,1), write(z,1), write(y,1)

[P2]: write(x,0), write(x,1), read(x,1), write(z,1), write(y,1)

[P3]: write(y,1), read(y,1), write(z,1), read(z,1), write(x,0), read(x,0)<sub>2</sub>, write(x,1)

Remark: The example is neither PRAM nor GWO nor PSO (and therefore neither PC-G nor PC-D nor causal) consistent which is shown in the corresponding sections.

Figure 3.1b shows an execution which is not cache consistent because the  $\mapsto$  relation requires the read(x,1) to happen before the write(x,3) and the write(x,2) after the write(x,3), which is not possible because write(x,2) <<sub>PO</sub> read(x,1).

Figure 3.2a cannot be cache consistent because  $\langle PO \cup \mapsto | (*, *, x, *)$  forms a cycle so that no Serialization may exist.

Figure 3.2e gives an example of an execution which is not cache consistent because no total order respecting  $\langle_{PO}$  on the operations regarding variable x can be formed: no matter which order is chosen for write(x,1) and write(x,2), it either conflicts with P1's or P3's operations.

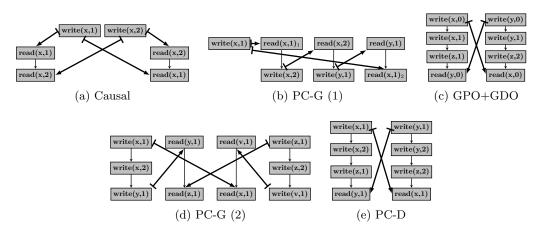

Figure 3.3a shows an execution which is not cache consistent because P2 and P3 see a different ordering of the writes, so that no total order of the operations regarding x is possible.

Figure 3.2c is not cache consistent because there exists no SerialView for x as write(x, 1) has to be ordered before write(x, 2) and read(x, 1) after write(x, 2).

#### 3.6. Global Write-read-write Order (GWO)

GWO was defined by Steinke and Nutt in their Unified theory of Shared Memory Consistency [StNu04]. They introduced the GWO property along with three other properties (GPO,GDO,GAO) which can be combined to define different consistency models.

**Definition 3.11.** Two writes are ordered by write-read-write order,  $w_1 <_{WO} w_2$ , iff there exists a read r, such that  $w_1 \mapsto r <_{PO} w_2$

**Definition 3.12.** An execution is Global Write-read-write Order (**GWO**) iff  $\forall_{i \in P} \exists SerialView (<_i \cup <_{WO} | (*, i, *, *) \cup (w, *, *, *))$

The write-read-write order orders two writes if a read exists which reads from the first write and is issued before the second write by the same processor. An execution is GWO if a process sees all writes which are ordered by write-read-write order in the given order along all own operations in the order it issued them.

**Example** Figure 3.2e gives an example of an execution which is GWO consistent:

[P1]: write(x,2), read(x,2), write(x,1), read(x,1) [P2]: write(x,1), write(x,2)

[P3]: write(x,1), read(x,1), write(x,2), read(x,2)

Remark: The example is neither PRAM nor Cache nor PSO (and therefore neither PC-G nor PC-D nor causal) consistent which is shown in the corresponding sections.

Figure 3.2a is not GWO consistent because  $<_0 \cup <_{WO} \cup \mapsto |(*, i, *, *) \cup (w, *, *, *)$  forms a cycle which excludes the existence of a SerialView.

Figure 3.2d shows an execution which is not GWO consistent as  $write(x, 0) <_{WO} write(x, 1) <_{WO} write(y, 1)$  and  $read(y, 1) < read(x, 0)_2$  exclude the existence of a SerialView.

An example for an execution which is not GWO is given in Figure 3.3b. It cannot be GWO consistent because write(x,1)  $<_{WO}$  write(x,2)  $<_{WO}$  write(z,1) which conflicts with read(z,1)  $<_i$  read(x,1).

Figure 3.4b shows another example of an execution which is not GWO consistent as no SerialView for P2 respecting  $write(x, 0) <_{WO} write(x, 1) <_{WO} write(y, 1)$  and  $read(y, 1) <_{PO} read(x, 0)$  can exist, the example cannot be GWO consistent.

The execution in Figure 3.4c is not GWO as  $write(y, 0) <_{WO} write(y, 1) <_{WO} write(x, 1) <_{WO} write(y, 2)$  prevents a SerialView of P1 which respects  $<_{WO}$  and  $<_i$ .

Figure 3.2c is not GWO consistent because there exists no SerialView for P3 as write(x, 1) has to be ordered before write(x, 2) and read(x, 1) after write(x, 2).

## 3.7. Global Anti-Order (GAO)

GAO was the fourth basic property defined by Steinke and Nutt [StNu04]. It is an extension to GDO, as they showed that GPO, GDO, and GWO together are not sufficient to describe sequential consistency. GPO+GAO+GWO however is equivalent to sequential consistency.

**Definition 3.13.** A Serial Order  $<_{SO}$  is a minimum partial order that satisfies:

$$\forall_{w,r\in O} \left( (var(w) = var(r) \land val(w) \neq val(r)) \Rightarrow \left( w <_{SO} w' \mapsto r \lor r <_{SO} w \right) \right)$$

**Definition 3.14.** Two writes are ordered by **Anti Order**,  $w_1 <_{AO(<_{SO})} w_2$ , iff

```

\exists_{r_1, r_2 \in O} \begin{bmatrix} w_1 \mapsto r_1 <_{PO} r_2 <_{DO} w_2 \\ \lor w_1 \mapsto r_1 <_{PO} r_2 <_{SO} w_2 \\ \lor w_1 \mapsto r_1 <_{SO} w_2 \\ \lor w_1 <_{PO} r_1 <_{DO} w_2 \\ \lor w_1 <_{PO} r_1 <_{SO} w_2 \end{bmatrix}

```

Definition 3.15. An execution is Global Anti-Order (GAO) iff

$\forall_{i \in P} \exists SerialView \left( \langle i \cup \langle SO \cup \langle AO(\langle SO \rangle) | (*, i, *, *) \cup (w, *, *, *) \right) \right)$

**Example** Figure 3.2f gives an example of an execution which is GAO consistent.

Remark: The example is not PSO consistent which is shown in the corresponding section.

Figure 3.4d gives an example of an execution that is not GAO consistent: For  $\langle SO \rangle$  only the pairs write(x, 1), read(x, 0) and write(y, 1), read(y, 0) and write(y, 0), read(y, 0) must be considered:

$$\begin{split} & write(x,1) <_{SO} write(x,0) \text{ conflicts with P1's } <_i \text{ so choose } read(x,0) <_{SO} write(x,1). \\ & write(y,1) <_{SO} write(y,0) \text{ conflicts with P2's } <_i \text{ so choose } read(y,0) <_{SO} write(y,1). \\ & read(y,1) <_{SO} write(y,0) \text{ with } <_i \text{ would not allow a SerialView for P1} \\ & \text{ so choose } write(y,0) <_{SO} write(y,1) \text{ instead.} \\ & write(x,0) <_{PO} write(x,1) <_{PO} read(y,0) <_{DO} write(y,1) \text{ leads to:} \\ & write(x,0) <_{AO(<_{SO})} write(y,1) \text{ and } write(x,1) <_{AO(<_{SO})} write(y,1) \\ & read(x,0) <_{SO} write(x,1), read(y,0) <_{SO} write(y,1) \text{ implies:} \\ & write(y,0) <_{AO(<_{SO})} write(y,1) \text{ and } write(x,0) <_{AO(<_{SO})} write(x,1) \\ & \text{ For P2: } <_{AO(<_{SO})} \text{ and } <_i \text{ require } write(x,0) \text{ to occur before } write(x,1) \text{ and } write(x,1) \text{ before } \\ & read(x,0) \text{ which excludes the existence of a SerialView which respects } <_{AO(<_{SO})} \text{ and } <_i. \end{split}$$

## 3.8. Causal Consistency / GPO+GWO

Causal memory is based on potential causality defined by Lamport [Lamp78] which defines a partial order on all memory operations. The partial order orders operations that are causally related, which enhances the former mentioned write-read-write order by process order (for other processes). Causal memory enforces that if a process writes a value after reading some writes' values, which potentially influenced the write, then all processes reading that write must have observed those other writes before as well.

The definition of causal consistency [ABHN91] taken from Steinke and Nutt [StNu04] is as follows:

Definition 3.16. An execution is causally consistent iff

$\forall_{i \in P} \exists SerialView (<_i \cup <_{PO} \cup <_{WO} | (*, i, *, *) \cup (w, *, *, *))$

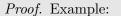

**Example** Figure 3.3a shows an execution which is causally consistent:

[P1]: write(x,1), read(x,1), write(x,2), read(x,2) [P2]: write(x,1), write(x,2)[P4]: write(x,2), read(x,2), write(x,1), read(x,1) [P3]: write(x,2), write(x,1)

Remark: The example is not cache consistent (and therefore not PC-G either) which is shown in the corresponding section.

#### 3.9. Processor Consistency by Goodman (PC-G)

Goodman gave a definition of processor consistency which is a consistency model stronger than both cache consistency and PRAM consistency but weaker than sequential consistency. As there exists multiple consistency models that differ slightly from Goodman's definition but are also called processor consistency the abbreviation PC-G is used for Goodman's definition.

Goodman's definition of processor consistency [Good91] and the equivalent GPO+GDO' consistency based on Theorem 3.4 from Steinke and Nutt [StNu04] is as follows:

Figure 3.3.: Examples for causally, PC-G, GPO+GDO, and PC-D consistent executions

Definition 3.17. An execution is processor consistent (PC-G) iff

$$\begin{aligned} \forall_{x \in V} \exists <_x = SerialView \left( <_{PO} | (*, *, x, *) \right) \\ \land \forall_{i \in P} \exists SerialView \left( \left( \cup_{x \in V} <_x \right) \bigcup <_{PO} | (*, i, *, *) \cup (w, *, *, *) \right) \end{aligned}$$

**Definition 3.18.** An order is an augmented data order  $<_{DO'}$  iff:  $<_{DO} \subseteq <_{DO'}$  and  $\forall_{o_1,o_2 \in O} (var(o_1) = var(o_2) \Rightarrow o_1 <_{DO'} o_2 \lor o_2 <_{DO'} o_1)$

Definition 3.19. An execution is GPO+GDO' iff

$$\forall_{i \in P} \exists SerialView (<_{PO} \cup <_{DO'} | (*, i, *, *) \cup (w, *, *, *))$$

**Example** An example for a PC-G consistent execution is given in Figure 3.3b:

[x]: write(x,1), read(x,1), read(x,1), write(x,2), read(x,2)

[y]: write(y,1), read(y,1)

[P1]: write(x,1), write(x,2), write(y,1)

[P2]: write(x,1), read(x,1), write(x,2), write(y,1)

[P3]: write(x,1), write(x,2), read(x,2), write(y,1)

[P4]: write(x,1), write(y,1), read(y,1), read<sub>2</sub>(x,1), write(x,2)

Remark: The example is neither GWO nor PSO consistent which is shown in the corresponding sections.

Figure 3.3d is PC-G consistent, because the required SerialViews exist:

$[x]: write(x,1), read(x,1), write(x,2) \quad [y]: write(y,1), read(y,1)$

[z]: write(z,1), read(z,1), write(z,2) [v]: write(v,1), read(v,1)

[P1]: write(x,1), write(x,2), write(y,1), write(z,1), write(z,2), write(v,1)

[P2]: write(x,1), write(x,2), write(y,1), read(y,1), write(z,1), read(z,1), write(z,2), write(v,1), write(z,2), write(z,2),

[P3]: write(z,1), write(z,2), write(v,1), read(v,1), write(x,1), read(x,1), write(x,2), write(y,1), write(x,2), write(y,1), write(x,2), write(y,1), write(x,2), write(y,1), write(x,2), write(y,1), write(x,2), write(x,2),

[P4]: write(z,1), write(z,2), write(v,1), write(x,1), write(x,2), write(y,1) = (P4)

Remark: The example is not PC-D consistent which is shown in the corresponding section.

Figure 3.3c cannot be PC-G because PC-G requires a total order on all operations on z, but if write(z, 1) is ordered before write(z, 2) then write(x, 1) would be ordered before read(x, 0), otherwise if write(z, 2) is ordered before write(z, 1) then write(y, 1) would be before read(y, 0).

Another example for an execution which is not PC-G is given in Figure 3.4c: PC-G requires a SerialView on each variable:

$[x]_1$ : write(x, 0), read(x, 0), write(x, 1), read(x, 1)

$[x]_2$ : write(x, 1), read(x, 1), write(x, 0), read(x, 0)

[y]: write(y,0), read(y,0), read(y,0), write(y,1), read(y,1), read(y,1), write(y,2), read(y,2), r

Neither one of the possible SerialViews  $[x]_1$  nor  $[x]_2$  allows P1 to have a SerialView that respects it together with [y] and  $\leq_{PO}$ . Therefore it cannot be PC-G.

Figure 3.3e is not PC-G consistent as there exists no SerialView for z which allows SerialViews for both processes. If write(z, 1) is ordered before write(z, 2) then no SerialView for P2 exists as  $write(x, 1) <_{PO} write(x, 2) <_{PO} write(z, 1)$  conflicts with  $write(z, 2) <_{PO} read(x, 1)$ , otherwise if write(z, 2) is ordered before write(z, 1) then no SerialView for P1 exists as  $write(y, 1) <_{PO} write(y, 2) <_{PO} write(z, 2)$  conflicts with  $write(z, 1) <_{PO} read(y, 1)$ . Therefore, the example cannot be PC-G consistent.

#### 3.10. GPO + GDO Consistency

GPO+GDO is a model described by Steinke and Nutt [StNu04] as combination of the properties GPO and GDO (PRAM and cache consistency). It is however not equivalent to PC-G as there exist executions which are GPO+GDO but not PC-G consistent. However, it is very close to PC-G, and Steinke and Nutt argue that GPO+GDO should be chosen as definition. The definition of GPO+GDO [StNu04] and an equivalent modified version of PC-G is as follows:

Definition 3.20. An execution is GPO+GDO iff

$\forall_{i \in P} \exists SerialView \left( \langle i \cup \langle PO \cup \langle DO | (*, i, *, *) \cup (w, *, *, *) \right) \right)$

Definition 3.21. An execution is PC-G' iff

$$\forall_{i \in P} \left( \forall_{x \in V} \exists <_x = SerialView \left( <_{PO} \middle| (*, *, x, *) \right) \\ \land \exists SerialView \left( \left( \cup_{x \in V} <_x \right) \bigcup <_{PO} \middle| (*, i, *, *) \cup (w, *, *, *) \right) \right)$$

An example for an execution which is GPO+GDO is given in Figure 3.3c.

Remark: The example is not PC-G which is shown in the corresponding section. It is also an example of a cache and PRAM consistent execution which is not PC-G.

## 3.11. Processor Consistency by DASH (PC-D)

The Stanford DASH multiprocessor system [LLGW<sup>+</sup>92] implements a variation of processor consistency hereafter called PC-D which is incomparable with PC-G [ABJK<sup>+</sup>93, GLLG<sup>+</sup>90]. Gharachorloo et al.'s [GLLG<sup>+</sup>90] definition differs from PC-G by weakening process order by allowing a process' read to outrun a write of the same process but on a different location. Furthermore PC-D enforces a different ordering on write operations.

View-based definition of PC-D [GLLG+90] by Ahamad et al. [ABJK+93]:

**Definition 3.22.** Two operations are ordered by weak-process-order,  $o_1 <_{wpo} o_2$ , iff

$o_1 <_{PO} o_2$   $\wedge (var(o_1) = var(o_2) \lor type(o_1) = type(o_2)$  $\lor (type(o_1) = r \land type(o_2) = w) \lor \exists_{o'} o_1 <_{wpo} o' <_{wpo} o_2)$

**Definition 3.23.** Two operations are ordered by weak-writes-before-order,  $o_1 <_{wwb} o_2$ , iff

$$type(o_1) = w \land type(o_2) = r \land \exists_{o'} (o_1 <_{wpo} o' \land o' \mapsto o_2)$$

**Definition 3.24.** Two operations are ordered by weak-reads-before-order,  $o_1 <_{wrb} o_2$ , with respect to the SerialViews  $<_x, x \in V$  iff

$$type(o_1) = r \wedge type(o_2) = w \land \exists_{o' \in (w, *, *, *)} (o_1(\bigcup_{x \in V} <_x)o' \land o' <_{wpo} o_2)$$

Definition 3.25. An execution is processor consistent (PC-D) iff

$\begin{array}{l} \forall_{x \in V} \exists <_x = Serial View \left( <_{PO} \right| \left( *, *, x, * \right) \right) \\ \land \forall_{i \in P} \exists Serial View \left( <_{wpo} \cup <_{wwb} \cup <_{wrb} \cup \left( \left( \cup_{x \in V} <_x \right) \right| \left( w, *, *, * \right) \right) | \left( *, i, *, * \right) \cup \left( w, *, *, * \right) \right) \\ \end{array}$

**Example** Figure 3.3e gives an example of a PC-D consistent execution.

#### 3.12. Partial Store Ordering (PSO)

Partial Store Ordering is one memory model used in SPARC architectures. It provides a better performance than the default TSO, but is defined as optional only in the architecture manual, so not all SPARC architectures may provide PSO. It allows to reorder writes after writes of different locations and writes after reads.

In the following, a simplified and modified axiomatic definition from the SPARC Architecture manual [SPAR91, SiFC92] for PSO [SPAR91] consistency is given. 'Simplified' means that the original definition uses 7 axioms, but three of them (Atomicity, Termination, StoreStore) are irrelevant for this consideration. Atomicity only concerns Swap operations which are not covered in this pure model definition of TSO, Termination gives a guarantee that a store will eventually be written to the memory and removed from the store buffer, and StoreStore considers STBAR instructions which are also not covered by this pure model definition. 'Modified' means that the axioms have been rewritten to fit the formalism used in this paper:

**Definition 3.26.** An execution is PSO if there exists a memory order  $\leq$  which respects:

- Order:  $(w, i, x, v_1) \le (w, j, y, v_2) \lor (w, i, y, v_2) \le (w, j, x, v_1)$

- Value:

$$val((r, i, a, x)) = val(Max_{\leq}[\{(w, j, a, y) | (w, j, a, y) <_{PO} (r, i, a, x)\} \cup \{(w, j, a, y) | (w, j, a, y) \leq (r, i, a, x)\}])$$

• LoadOp:

$$r \in (r, i, *, *), o \in (*, i, *, *)$$

$r <_{PO} o \Rightarrow r \le o$

• StoreStoreEq:  $\forall_{x \in V} \forall_{w_1, w_2 \in (write, i, x, *)} w_1 <_{PO} w_2 \Rightarrow w_1 \leq w_2$

PSO consistency is best explained by describing a possible computer architecture: Each process has a store buffer for each memory location which buffers writes before writing them to memory. If a process reads a location for which a write exists in the corresponding store buffer then it reads the latest write's value from that store buffer, otherwise it reads the value from memory.

An execution is PSO consistent if a process observes its own operations in program order and there exists a total order on all write operations which is observed by all processes regarding others' writes. Also a process may not observe all writes of other processes as these may be hidden by own writes in its store buffer.

**Example** Figure 3.4a shows an example of an execution which is PSO consistent what can easily be seen if write(x, 0) is buffered by P1.

Remark: The example is not PRAM consistent which is shown in the corresponding section. It can be seen that the execution in Figure 3.4b is PSO consistent if write(x, 1) is buffered by P1.

Remark: The example is not GWO consistent which is shown in the corresponding section.

Figure 3.2d shows an execution which is not PSO consistent because P3 has no writes and

Figure 3.4.: Examples for PSO, and TSO consistent executions

this way no writes may be hidden and therefore it is implied that read(x, 1) appears before  $read(x, 0)_2$  in the Serialization which therefore cannot be a SerialView.

Figure 3.2e gives an example of an execution which is not PSO as P1 and P3 have different views on the writes of P2 where no serialization  $\leq_W$  on all writes may exist.

Figure 3.2f gives another example of an execution which is not PSO consistent because if P2 reads write(x, 1), both writes of P1 have already been written to main memory and if P3 reads write(y, 1) all three writes of P1 and P2 have also been written to memory, therefore P3 cannot read write(x, 0).

Another example for an execution which is not PSO is given in Figure 3.3b.

## 3.13. Total Store Ordering (TSO)

Total Store Ordering is the default memory model of SPARC architectures. The SPARC architecture manual [SPAR91] states that every implementation has to offer TSO. TSO allows the reordering of stores after loads.

In the following a simplified and modified axiomatic definition by [SPAR91, SiFC92] for TSO [SPAR91] consistency is given. 'Simplified' means that the original definition uses 6 axioms, but two of them (Atomicity, Termination) are irrelevant for this consideration. Atomicity only concerns Swap operations which are not covered in this definition of TSO and Termination gives a guarantee that a store will eventually be written to the memory and removed from the store buffer. 'Modified' means that the axioms have been rewritten to fit the formalism used in this paper:

**Definition 3.27.** An execution is TSO if there exists a memory order  $\leq$  which respects:

- Order:  $(w, i, x, v_1) \le (w, j, y, v_2) \lor (w, i, y, v_2) \le (w, j, x, v_1)$

- Value:

$$val((r, i, a, x)) = val(Max_{\leq}[\{(w, j, a, y) | (w, j, a, y) <_{PO} (r, i, a, x)\} \cup \{(w, j, a, y) | (w, j, a, y) \leq (r, i, a, x)\}])$$

- LoadOp:  $r \in (r,i,*,*), o \in (*,i,*,*)$   $r <_{PO} o \Rightarrow r \leq o$

- StoreStore:  $w_1, w_2 \in (write, i, *, *) \ w_1 <_{PO} w_2 \Rightarrow w_1 \le w_2$

A view-based definition of TSO [SPAR91] consistency based on the axioms in [SPAR91, SiFC92, LoCM06] is proposed as follows:

#### Definition 3.28.

$$W_{Inv}^{(i)} = \left\{ w \mid proc(w) \neq i \land \nexists r \in (r, i, *, *) : w \mapsto r \\ \land \left[ \exists w' \in (w, i, *, *) : w <_W w' \land var(w) = var(w') \\ \land \nexists w'' \in (w, j, *, *), j \neq i, r \in (r, i, *, *) : w <_W w'' <_W w' \land w'' \mapsto r \land r <_i w' \right] \right\}$$

Proposition 3.1. An execution is TSO consistent iff

$$\exists <_W = SerialView (<_{PO}|(w, *, *, *)) \\ \land \\ \forall_{i \in P} \exists SerialView \left( <_i \cup (<_W \setminus (w, *, *, *) \times (w, i, *, *)) \middle| \left( (w, *, *, *) \setminus W_{inv}^{(i)} \right) \cup (*, i, *, *) \right)$$

TSO consistency is best explained by describing a possible architecture: Each process has a store buffer which buffers writes before writing them to memory in order. If a process reads a location for which a write exists in its store buffer, then it reads the latest value from the store buffer, otherwise it reads the value from memory.

An execution is TSO consistent if a process observes its own operations in program order and there exists a total order on all write operations which respects program order and is observed by all processes regarding others' writes. Also a process may not observe all writes of other processes as they may be hidden by own writes in its store buffer.

**Example** An example for a TSO consistent execution is given in Figure 3.4c. It can be easily seen that the example is TSO consistent if only write(x, 0) is buffered.

Remark: The example is neither PC-G nor GWO consistent which is shown in the corresponding sections.

Figure 3.4d gives an example of an execution that is TSO consistent. If only write(x, 1) is kept in the store buffer then it is clear that the execution is TSO.

Remark: The example is not GAO consistent which is shown in the corresponding section.

#### 3.14. Sequential Consistency (SC)

Sequential consistency was defined by Lamport [Lamp79]. He states that an execution on a multiprocessor system may not produce the desired results while each process itself executes its program correctly. Therefore he introduces two implementation requirements which enforce sequential consistency:

• R1: Each processor issues memory requests in the order specified by its program.

• R2: Memory request from all processors issued to an individual memory module are serviced from a single FIFO queue. Issuing a memory request consists of entering the request in this queue.

The definition of sequential consistency [Lamp79] according to [StNu04] is:

**Definition 3.29.** An execution is sequentially consistent iff  $\exists SerialView(<_{PO})$

A system is sequentially consistent if for all executions, there exists a sequential order which respects process order and leads to the same result as the execution.

**Example** Figure 3.1c gives an example of a sequentially consistent execution. It is SC as the following SerialView respecting  $\langle_{PO}$  exists: write(x, 1), read(x, 1), write(y, 1), read(y, 1).

# 3.15. Overview/Relationship

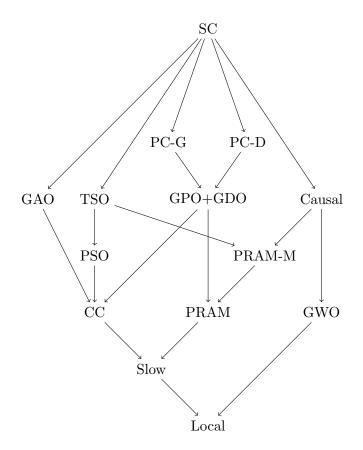

Figure 3.5.: Relationship overview over the presented consistency models

Figure 3.5 illustrates the relationship between the described consistency models. An arrow indicates that the model the arrow originates from implies the model the arrow points at. A model implies an other model if all executions accepted by this model are excepted by the other one.

The relationship of local, slow, PRAM (GPO), cache (GDO), GWO, causal (GPO+GWO), GPO+GDO and sequential consistency is shown by Steinke and Nutt [StNu04].

In the following, the relationship of PSO and TSO to the other models is shown.

#### 3.15.1. PSO

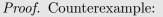

**Theorem 3.1.**  $TSO \Rightarrow PSO$  : all TSO consistent executions are PSO consistent.

*Proof.* It is easy to see that a TSO system behaves like a PSO system which writes values from its store buffers to main memory in the same order the process' single store buffer

of the TSO system does.

**Theorem 3.2.**  $PSO \neq TSO$  : some PSO consistent executions are not TSO consistent.

*Proof.* Figure 3.4b gives a counterexample which is PSO consistent but not TSO consistent, it is explained in Section 3.12 that the example is PSO. It cannot be TSO because when P2 reads the value of write(y, 1) all of P1's writes must have been written back from the store buffer, therefore P2 observes  $write(x, 0) <_{PO} write(x, 1)$  and cannot observe read(x, 0) afterwards.

**Theorem 3.3.**  $PSO \Rightarrow CC$  : all PSO consistent executions are cache consistent.

*Proof.* Assume a PSO consistent execution. Then the main memory sees a sequential order  $<_W$  of all writes and all unbuffered reads. If all operations from this order are excluded except the operations regarding variable x, then the resulting order  $<_W^x$  clearly respects  $<_{PO}$ . If  $<_{PO}$  is limited to only operations regarding variable x then buffered reads always follow the corresponding writes without any other intermediate operations regarding xin between. If those buffered reads are inserted directly after their corresponding write into  $<_W^x$ , then the resulting order  $<_x$  is a sequentialization of all operations regarding xwhich respects  $<_{PO}$ . Therefore, the execution is cache consistent.

**Theorem 3.4.**  $CC \Rightarrow PSO$  - some cache consistent executions are not PSO consistent.

*Proof.* Figure 3.2d shows an example of an execution which is cache consistent but not PSO consistent, which is explained in Section 3.5 and 3.12.  $\Box$

**Theorem 3.5.**  $PSO \Rightarrow PRAM$  - some PSO consistent executions are not PRAM consistent.

*Proof.* Figure 3.4a shows an example of an execution which is PSO consistent but not PRAM consistent, which is explained in Section 3.12 and 3.3.  $\Box$

**Theorem 3.6.**  $PRAM \neq PSO$  - some PRAM consistent executions are not PSO consistent.

*Proof.* Assuming  $PRAM \Rightarrow PSO$ . Using  $PSO \Rightarrow CC$  follows  $PRAM \Rightarrow CC \notin$  because PRAM is incomparable to CC as seen in the examples at Sections 3.5 and 3.3. Therefore, the assumption must be incorrect.

**Theorem 3.7.**  $PSO \Rightarrow GWO$  - some PSO consistent executions are not GWO consistent.

*Proof.* Figure 3.4b shows an example of an execution which is PSO consistent, but not GWO consistent, which is explained in Sections 3.12 and 3.6.  $\Box$

**Theorem 3.8.**  $GWO \Rightarrow PSO$  - some GWO consistent executions are not PSO consistent.

*Proof.* Assuming  $GWO \Rightarrow PSO$ . Using  $PSO \Rightarrow CC$  follows  $GWO \Rightarrow CC \notin$  because GWO is incomparable to CC as seen in the examples at Sections 3.5 and 3.6. Therefore, the assumption must be incorrect.

**Theorem 3.9.**  $PSO \neq GAO$  - some PSO consistent executions are not GAO consistent.

The example is clearly PSO if only write(x,1) is kept in the corresponding store buffer. It is not GAO because  $write(x,0) <_{PO} read(x,0) <_{DO} write(x,1) <_{PO} read(y,\perp) <_{DO} write(y,1)$  implies  $write(x,0) <_{AO(<_{SO})} write(x,1) <_{AO(<_{SO})} write(y,1)$ , and thus no SerialView for P2 exists which respects  $<_{AO(<_{SO})}$  and  $<_i$  as  $read(y,1) <_i read(x,0)$  conflicts with the mentioned  $<_{AO(<_{SO})}$ .

**Theorem 3.10.**  $GAO \neq PSO$  - some GAO consistent executions are not PSO consistent.

*Proof.* Figure 3.2f shows an example of an execution which is GAO consistent, but not PSO consistent, which is explained in Sections 3.7 and 3.12.  $\Box$

#### 3.15.2. TSO

**Theorem 3.11.**  $TSO \Rightarrow PRAM$  - all TSO consistent executions are PRAM consistent.

*Proof.* Assuming TSO consistency.

TSO implies the existence of a total order  $<_W$  on all writes which respects  $<_{PO}$ . As every process sees its own writes in program order  $<_i$  and all other processes' write in order  $<_W$ , it is implied that every process sees all writes in an order which respects  $<_{PO}$  which implies PRAM consistency.

**Theorem 3.12.**  $PRAM \Rightarrow TSO$  - some PRAM consistent executions are not TSO consistent.

*Proof.* Assuming  $PRAM \Rightarrow TSO$ . Using  $TSO \Rightarrow PSO$  and  $PSO \Rightarrow CC$  follows  $PRAM \Rightarrow CC \notin$  because PRAM is incomparable to CC as seen in the examples at Sections 3.5 and 3.3. Therefore, the assumption must be incorrect.  $\Box$

**Theorem 3.13.**  $TSO \Rightarrow GWO$  - some TSO consistent executions are not GWO consistent.

*Proof.* Figure 3.4c shows an example of an execution which is TSO consistent, but not GWO consistent, which is explained in Sections 3.13 and 3.6.  $\Box$

**Theorem 3.14.**  $GWO \neq TSO$  - some GWO consistent executions are not TSO consistent.

*Proof.* Assuming  $GWO \Rightarrow TSO$ . Using  $TSO \Rightarrow PSO$  follows  $GAO \Rightarrow PSO$ .  $\notin$  This assumption is incorrect as it would conflict with  $GWO \Rightarrow PSO$  shown in Theorem 3.8

**Theorem 3.15.**  $GAO \Rightarrow TSO$  - some GAO consistent executions are not TSO consistent.

*Proof.* Assuming  $GAO \Rightarrow TSO$ . Using  $TSO \Rightarrow PSO$  follows  $GAO \Rightarrow PSO$ .  $\notin$  This assumption is incorrect as it would conflict with  $GAO \Rightarrow PSO$  shown in Theorem 3.10  $\Box$

**Theorem 3.16.**  $TSO \Rightarrow GAO$  - some TSO consistent executions are not GAO consistent.

*Proof.* Figure 3.4d shows an example of an execution which is TSO consistent, but not GAO consistent, which is explained in Sections 3.13 and 3.7.  $\Box$

**Theorem 3.17.**  $TSO \neq PC$ -G - some TSO consistent executions are not PC-G consistent.

*Proof.* Figure 3.4c shows an example of an execution which is TSO consistent, but not PC-G consistent, which is explained in Sections 3.13 and 3.9.  $\Box$

#### 3.15.3. PRAM-M

**Theorem 3.18.**  $PRAM-M \Rightarrow PRAM$  - all PRAM-M consistent executions are PRAM consistent.

*Proof.* Consider a PRAM-M consistent execution, then there exists a SerialView on own operations and others' writes which respects  $<_{PO} \cup <_{lwo}^{(i)}$  for each process. A SerialView respecting  $<_{PO} \cup <_{lwo}^{(i)}$  obiously respects  $<_{PO}$  as well. Therefore, all PRAM-M consistent executions must be PRAM consistent.

**Theorem 3.19.**  $PRAM \neq PRAM-M$  - some PRAM consistent executions are not PRAM-M consistent.

*Proof.* Figure 3.2b shows an example of an execution which is PRAM consistent, but not PRAM-M consistent, which is explained in Sections 3.3 and 3.4.  $\Box$

**Theorem 3.20.**  $PRAM-M \Rightarrow CC$  - some PRAM-M consistent executions are not CC consistent.

*Proof.* Figure 3.2c shows an example of an execution which is PRAM-M consistent, but not CC consistent, which is explained in Sections 3.4 and 3.5.  $\Box$

**Theorem 3.21.**  $CC \Rightarrow PRAM-M$  - some CC consistent executions are not PRAM-M consistent.

*Proof.* Assuming  $CC \Rightarrow PRAM$ -M. Using PRAM-M  $\Rightarrow PRAM$  follows  $CC \Rightarrow PRAM$ .  $\notin$  This assumption is incorrect as PRAM is incomparable to CC as seen in the examples at Sections 3.5 and 3.3.

**Theorem 3.22.**  $PRAM-M \Rightarrow GWO$  - some PRAM-M consistent executions are not GWO consistent.

*Proof.* Figure 3.2c shows an example of an execution which is PRAM-M consistent, but not GWO consistent, which is explained in Sections 3.4 and 3.6.  $\Box$

**Theorem 3.23.**  $GWO \neq PRAM-M$  - some GWO consistent executions are not PRAM-M consistent.

*Proof.* Assuming  $GWO \Rightarrow PRAM-M$ . Using PRAM-M  $\Rightarrow PRAM$  follows  $GWO \Rightarrow PRAM$ .  $\notin$  This assumption is incorrect as PRAM is incomparable to GWO as seen in the examples at Sections 3.6 and 3.3.

**Theorem 3.24.**  $PC-G \Rightarrow PRAM-M$  - some PC-G (and therefore GPO+GDO) consistent executions are not PRAM-M consistent.

The example is PC-G consistent and therefore GPO+GDO consistent as well:

$\begin{array}{l} [x]: \ write(x,1), read(x,1)_1, read(x,1)_2, write(x,2), read(x,2) \\ [y]: \ write(y,1), read(y,1) \\ [P1]: \ write(x,1), write(y,1), read(y,1), read(x,1)_2, write(x,2) \\ [P2]: \ write(x,1), read(x,1), write(x,2), write(y,1) \\ [P3]: \ write(x,1), write(x,2), read(x,2), write(y,1) \\ \end{array}$

But not PRAM-M as for P1:  $write(x,1) <_{lwo}^{(i)} write(x,2) <_{lwo}^{(i)} write(y,1)$  allows no SerialView with  $write(x,1) <_i read(y,1) <_i read(x,1)_2$

**Theorem 3.25.**  $PSO \neq PRAM-M$  - some PSO consistent executions are not PRAM-M consistent.

The example is PSO consistent as it can be easily seen if write(y, 1) is buffered.

But not PRAM-M as for P1:  $write(y,1) <_{lwo}^{(i)} write(y,2) <_{lwo}^{(i)} write(x,2)$  allows no SerialView with  $write(y,1) <_i write(x,1) <_i read(x,2) <_i read(y,1)_2$

**Proposition 3.2.**  $Causal \Rightarrow PRAM-M$  - all causal consistent executions are PRAM-M consistent.

**Proposition 3.3.**  $TSO \Rightarrow PRAM-M$  - all TSO consistent executions are PRAM-M consistent.

#### 3.15.4. PC-D

**Theorem 3.26.**  $PC-D \Rightarrow PC-G$  - some PC-D consistent executions are not PC-G consistent.

*Proof.* Figure 3.3e shows an example of an execution which is PC-D consistent, but not PC-G consistent, which is explained in Sections 3.11 and 3.9.  $\Box$

**Theorem 3.27.**  $PC-G \Rightarrow PC-D$  - some PC-G consistent executions are not PC-D consistent.

*Proof.* Figure 3.3d shows an example of an execution which is PC-G consistent, but not PC-D consistent, which is explained in Sections 3.9 and 3.11.  $\Box$

**Proposition 3.4.** PC-D  $\Rightarrow$  *GPO*+*GDO* - all PC-D consistent executions are GPO+GDO consistent.

**Proposition 3.5.**  $GPO + GDO \Rightarrow$  PC-D - some GPO+GDO consistent executions are not PC-D consistent.

**Proposition 3.6.**  $TSO \Rightarrow PC-D$  - some TSO (and therefore PSO) consistent executions are not PC-D consistent.

**Proposition 3.7.** Causal  $\Rightarrow$  PC-D - some causally consistent executions are not PC-D consistent.

### 3. Consistency Models

# 4. Reference Machines

Given the set of processes P, shared variables V, operations O and the process order  $\leq_{PO}$  an implementation of a memory system determines the writes-to order  $\mapsto$ , from which the read values can be derived.

In this chapter, reference machines for different memory consistency models are introduced. These machines determine for each input  $(P,V,O,\leq_{PO})$  a writes-to order which is consistent with its memory consistency model. Furthermore, it is shown that the machines cover every possible writes-to order which is consistent with its memory model for a given input.

These reference machines illustrate the definition of different memory models in an operational way.

## 4.1. Common Structural Elements

The reference machines are constructed by components which are introduced in the following.

## 4.1.1. FIFO

The FIFO component is a First-In-First-Out Buffer which buffers memory operations as tuples. It holds the operation type (read or write), the issuing process' id, the memory address, and in case of a write operation the value to be written.

The FIFO component is considered to be an unbounded buffer for completeness proofs. It can be bounded for finite operation sets. Boundedness is further discussed in Section 5.4.

An implementation is given as Quartz code in Appendix A.2.1. The implementation is bounded because of programming language restrictions.

#### 4.1.2. FIFOwClock

FIFOwClock is an extended FIFO buffer which endores entries by an additional clock value. A clock value is a natural number which is considered unbounded for theoretical purposes.

An implementation is given as Quartz code in Appendix A.2.2. In the implementation the clock value is a bounded natural number because of programming language restrictions.

## 4.1.3. FIFOwClocks

FIFOwClocks is an extended FIFOwClock buffer which does not only contain one clock for each entry, but N clocks, where N is the number of processes. An implementation is given as Quartz code in Appendix A.2.3.

## 4.1.4. FIFOwReadForwarding

The FIFOwReadForwarding components is a FIFO buffer which is extended by a read forwarding mechanism. This mechanism enables to check if an entry regarding a given memory location is present in the buffer and if so to obtain that entries value. An implementation is given as Quartz code in Appendix A.2.4.

## 4.1.5. MemUnit

The MemUnit component represents a memory unit which stores values to a given location and retrieves the last written values on a read operation. An implementation is given as Quartz code in Appendix A.2.5.

## 4.1.6. MemUnitSingleCell

MemUnitSingleCell behaves equivalent to MemUnit but consists only of one memory cell which corresponds to a single memory location. An implementation is given as Quartz code in Appendix A.2.6.

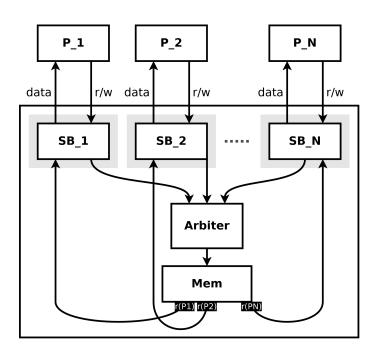

## 4.1.7. Store Buffer (SB)

Store buffers (SB) consist of a MemUnitSingleCell component and additional logic. It receives memory operations and inserts writes into the MemUnitSingleCell and forwards them to the arbiter if requested. On received read operations it checks the MemUnitSingleCell if it contains a write to that memory location and returns the latest one if it exists and otherwise forwards the read to the arbiter if requested.

## 4.1.8. Distributor (Dist)

A distributor (Dist) is responsible for distributing memory operations to the connected components while respecting some rules. As these rules differ from memory model to memory model, the semantics and implementations differ for each model.

### 4.1.9. Arbiter

The arbiter is typically the characterising component of a memory model. It determines the order in which memory operations are passed from the connected components based on consistency model dependent rules.

If it chooses a component which is not ready to deliver an operation (e.g. in case of an empty FIFO) the arbiter is considered to idle and to make a new choice in the next cycle. This behaviour could be optimized but is required to achieve the completeness property.

The arbiter's behaviour of most models differ significantly and therefore the implementations are model specific.

### 4.1.10. Receiver (Rec)

A receiver (Rec) is responsible to receive read results from multiple components and to deliver them to its process.

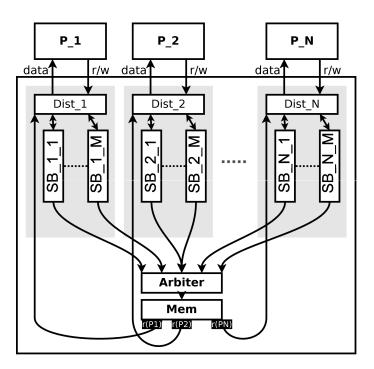

## 4.2. Local Consistency Reference Machine

#### 4.2.1. Structure

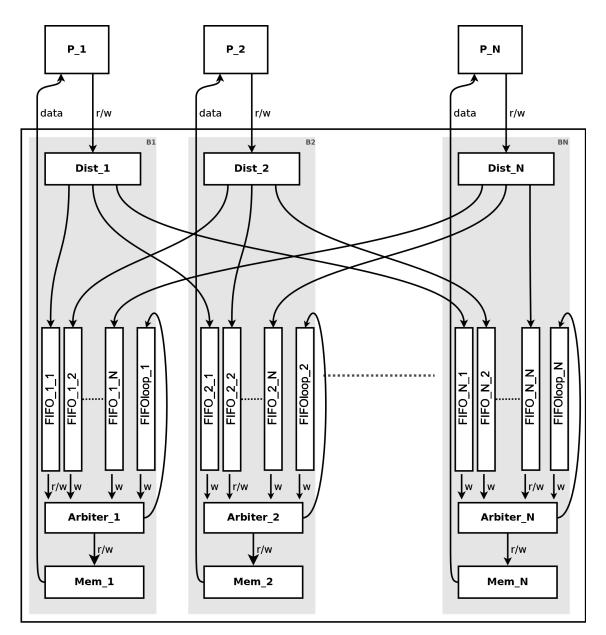

The structure of the local consistency reference machine is shown in Figure 4.1 for a given set P of n processes and m memory locations. For each process  $P_i \in P$  the memory system has a distributor  $Dist_i$ , an arbiter  $Arbiter_i$ , a memory unit  $Mem_i$  and n different FIFO buffers  $FIFO_{i,j}, j \in \{1 \dots n\}$  and an additional FIFO buffer  $FIFOloop_i$ . A distributor  $Dist_i$ broadcasts received writes to all corresponding FIFOs  $FIFO_{j,i}, j \in \{1 \dots n\}$ , and sends all received reads to the FIFO  $FIFO_{i,i}$ . The arbiters choose non-deterministically from the connected FIFOs to read from. If  $Arbiter_i$  selected  $FIFO_{i,i}$  the operation is passed to the memory unit. If any other  $FIFO_{i,j}, i \neq j$  or  $FIFO_{loop_i}$  is selected then the arbiter chooses non-deterministically to either pass it to the memory unit or to insert it in  $FIFO_{loop_i}$ .

## 4.2.2. Correctness

**Theorem 4.1.** The given reference machine is correct: All executions it may produce for a given input are Local consistent.

*Proof.* For each process, its arbiter generates a SerialView while maintaining  $\langle i \rangle$ . The own memory commands are kept in order in the FIFO and are sent directly in order to the memory if the corresponding FIFO is selected. The SerialView covers all own operations and all write operations as no write is lost, writes from other processes are inserted into their corresponding FIFO and either send to the memory unit or put in the feedback FIFO until further processing from there.

#### 4.2.3. Completeness

**Theorem 4.2.** The given reference machine is complete: For a given input, it covers every Local consistent execution.

*Proof.* Consider a local consistent execution (by Definition 3.2):

$\forall_{i \in P} \exists SerialView (<_i | (*, i, *, *) \cup (w, *, *, *))$

As the arbiter selects nondeterministically, it may use its process SerialView (which must exist according to the definition) as selection criteria: If according to the SerialView, operation  $\tilde{o}$  is to be processed next, it moves operations from the corresponding FIFO into the feedback FIFO until it fetches  $\tilde{o}$  which it passed to the memory unit. Using this selection order, the resulting writes-to order  $\mapsto$  is the same as the one of the assumed

Figure 4.1.: Local consistency reference machine

$\square$

execution. Therefore every Local consistent execution is covered by the reference machine.

## 4.3. Slow Consistency Reference Machine

## 4.3.1. Structure

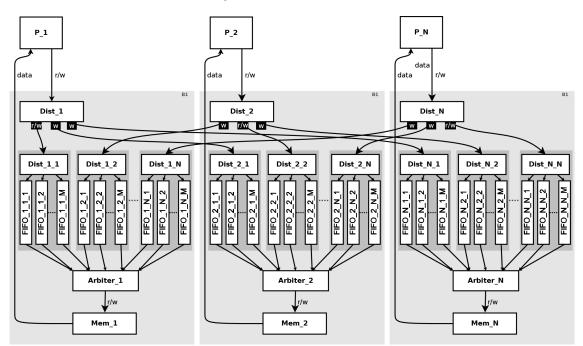

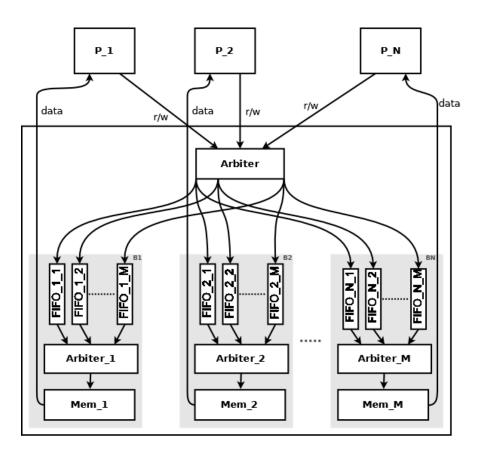

The structure of the slow consistency reference machine is shown in Figure 4.2 for a given set P of n processes and m memory locations. For each process  $P_i \in P$  the memory system has a distributor  $Dist_i$  and n different distributors  $Dist_{i,j}, j \in \{1 \dots n\}$ , an arbitre  $Arbiter_i$ , a memory unit  $Mem_i$  and  $n \times m$  different FIFO buffers  $FIFO_{i,j,k}, j \in \{1 \dots n\}, k \in \{1 \dots m\}$ . A distributor  $Dist_i$  broadcasts received writes to all corresponding distributors  $Dist_{j,i}, j \in \{1 \dots n\}$ , and sends all received reads to the distributor  $Dist_{i,i}$ . A sub-distributor  $Dist_{i,j}$  broadcasts received memory cell k to the corresponding FIFO  $FIFO_{i,j,k}$ . The arbiters choose non-deterministically one of the connected FIFOs to read from.

Figure 4.2.: Slow consistency reference machine

### 4.3.2. Correctness

**Theorem 4.3.** The given reference machine is correct: All executions it may produce for a given input are slowly consistent.

*Proof.* The distributor fills the FIFOs in the order of the incoming memory operations. Usage of FIFO buffers ensures by construction that the read and write operations of each process are kept in order for each memory location (maintains  $\leq_{PO}$   $|(*, i, x, *) \cup (w, *, x, *)\rangle$ . The arbiter takes elements from the top of a FIFO buffer and issues the operation to the memory unit. Therefore, the memory unit has a serial view on all processes' write operations and the read operations of its corresponding process, and because this property holds for each memory unit, the execution, consisting of  $(P, V, O, \leq_{PO}, \mapsto)$ , is slowly consistent according to Definition 3.3.

#### 4.3.3. Completeness

**Theorem 4.4.** The given reference machine is complete: For a given input, it covers every slowly consistent execution.

*Proof.* Consider a slowly consistent execution (by Definition 3.3):

$\forall_{i \in P, x \in V} \exists SerialView(\leq_{PO} | (*, i, x, *) \cup (w, *, x, *))$

If each arbiter uses the SerialViews (one for each memory location) of its process (which exist according to the definition) as selection order (which is a valid selection order because the arbiter chooses non-deterministically), then the resulting writes-to order  $\mapsto$  is the same as the one of the assumed execution.  $\notin$  Therefore every slowly consistent execution is covered by the reference machine.

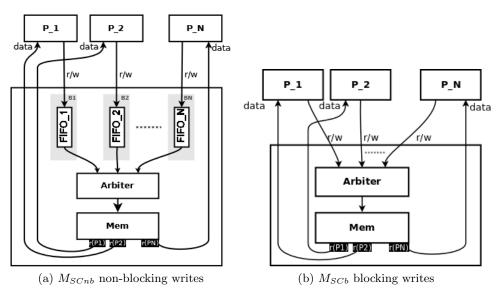

## 4.4. PRAM Consistency Reference Machine

$M_{PRAM}$  shows a possible implementation of PRAM consistency (Section 3.3). The model suits for distributed systems as seen in  $M_{PRAM}$  because each process has its own local memory. Another advantage for use in distributed system is the lack of transmission delay dependencies: no process has to wait for the arrival of another process' write to proceed.

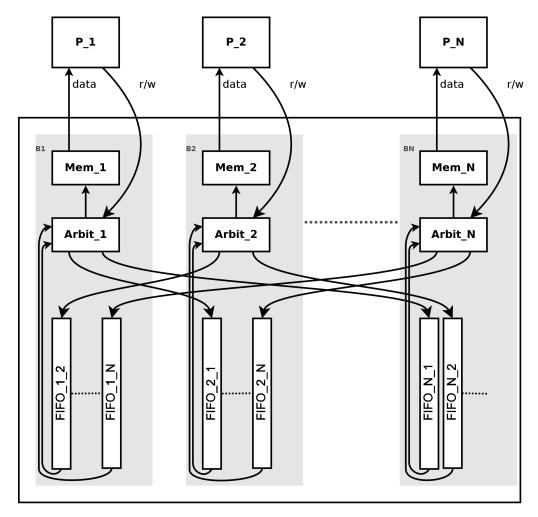

#### 4.4.1. Structure

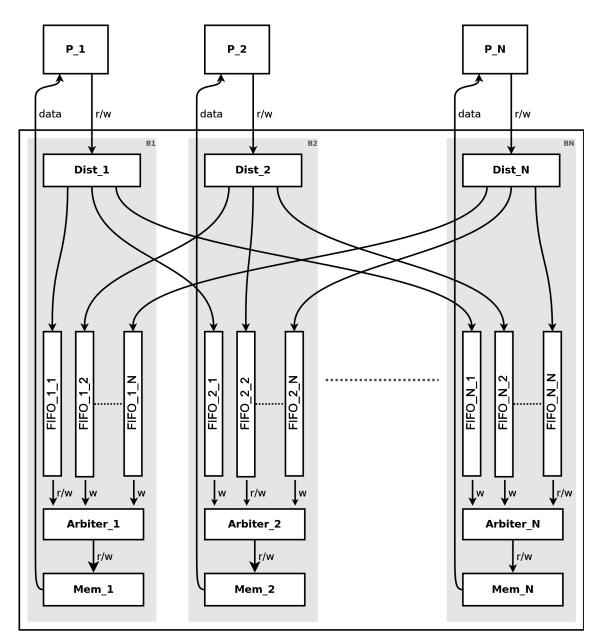

The structure of the PRAM consistency reference machine is shown in Figure 4.3 for a given set P of n processes. For each process  $P_i \in P$  the memory system has a distributor  $Dist_i$ , an arbiter  $Arbiter_i$ , a memory unit  $Mem_i$  and n different FIFO buffers  $FIFO_{i,j}, j \in \{1...n\}$ . A distributor  $Dist_i$  broadcasts received writes to all corresponding FIFOs  $FIFO_{j,i}, j \in \{1...n\}$ , and sends all received reads to the FIFO  $FIFO_{i,i}$ . The arbiters choose non-deterministically from the connected FIFOs to read from.